Titan-2

Titan-2 Family FPGAs use advanced and mature processes, supporting high-performance modules and interfaces such as SERDES high-speed interfaces, PCIe Gen3, and DDR3/4. It provides customers with high-performance programmable solutions, which can be widely applied in industries such as communications, image and video processing, data analysis, network information security, and instrumentation.

Product Features

Product Selection Guide

| Part Number | PG2T70H | PG2T160H | PG2T390H1 | PG2T390HX | ||

| Logic elements | logic Cell | 68160 | 165120 | 389760 | 389760 | |

| LUTs | 42600 | 103200 | 243600 | 243600 | ||

| Flip-Flop | 85200 | 206400 | 487200 | 487200 | ||

| RAM resources | Distributed RAM (Kbit) | 843.75 | 2187 | 4712 | 4712 | |

| Block RAM (36Kbit each) | 135 | 350 | 480 | 480 | ||

| Total block RAM (Kbit) | 4860 | 12600 | 17280 | 17280 | ||

| Clock resources | GPLL+PPLL | 6+6 | 8+8 | 10+10 | 10+10 | |

| IO resources | Max. user I/O | 300 | 400 | 500 | 500 | |

| Max. differential I/O(pairs) | 144 | 192 | 240 | 240 | ||

| DDR3/4(Mbps) | 1866 | 1866 | 1866 | 1866 | ||

| Hard core resources | APM 25*18 | 240 | 600 | 840 | 840 | |

| ADC/Monitor hard cores | 12 | 12 | 1 | 1 | ||

| PCIE Gen3x8 | 0 | 1 | 1 | 1 | ||

| PCIE Gen2x8 | 1 | 0 | 0 | 0 | ||

| HSST(13.125Gbps) Lane | 8 | 8 | 16 | 16 | ||

| Package | Dimensions(mm) | Ball Pitch(mm) | HRIO(3.3V)/HPIO(1.8V)/HSST | |||

| FBB484 | 23*23 | 1 | 185/100/4 | 185/100/4 | ||

| FBB676 | 27*27 | 1 | 200/100/8 | |||

| FFBG676 | 27*27 | 1 | 250/150/8 | 250/150/8 | 250/150/8 | |

| FFBG900 | 31*31 | 1 | 350/150/16 | 350/150/16 | ||

| Note: 1、Titan-2 HRIO supports 1.25Gbps LVDS, and its HPIO supports 1.5Gbps LVDS. Except for PG2T390H, whose HRIO supports 1.0Gbps LVDS and HPIO supports 1.4Gbps LVDS. 2、PG2T160H and PG2T70H support Monitor hard cores, while PG2T390H and PG2T390HX support ADC hard cores. |

||||||

Technical Documentation

-

PK05007_PG2T160H-FBB484_V0.1

PK05007_PG2T160H-FBB484_V0.1 2025.09.17

2025.09.17

-

PK05006_PG2T160H-FFBG676_V0.2

PK05006_PG2T160H-FFBG676_V0.2 2025.09.17

2025.09.17

-

PK05005_PG2T70H-FBB676_V0.1

PK05005_PG2T70H-FBB676_V0.1 2025.09.17

2025.09.17

-

PK05004_PG2T70H-FBB484_V0.2

PK05004_PG2T70H-FBB484_V0.2 2025.09.17

2025.09.17

-

PK05002_PG2T390H_FFBG676_V1.4

PK05002_PG2T390H_FFBG676_V1.4 2025.09.17

2025.09.17

-

PK05001_PG2T390H_FFBG900_V1.6

PK05001_PG2T390H_FFBG900_V1.6 2025.09.17

2025.09.17

-

UG050012_Titan2 Family Hardware Design Guide_V1.5

UG050012_Titan2 Family Hardware Design Guide_V1.5 2025.09.17

2025.09.17

-

UG050010_Titan2 Family FPGAs Monitor User Guide_V1.1

UG050010_Titan2 Family FPGAs Monitor User Guide_V1.1 2025.09.17

2025.09.17

-

UG050009_Titan2 Family FPGAs Analog-to-Digital Converter (ADC) Module User Guide_V1.2

UG050009_Titan2 Family FPGAs Analog-to-Digital Converter (ADC) Module User Guide_V1.2 2025.09.17

2025.09.17

-

UG050008_Titan2 Family FPGAs High-Speed Serial Transceiver (HSSTHP) User Guide_V1.4

UG050008_Titan2 Family FPGAs High-Speed Serial Transceiver (HSSTHP) User Guide_V1.4 2025.09.17

2025.09.17

-

UG050007_Titan2 Family FPGAs GTP User Guide_V1.1

UG050007_Titan2 Family FPGAs GTP User Guide_V1.1 2025.09.17

2025.09.17

-

UG050006_Titan2 Family FPGAs InputOutput Interface (IO) UserGuide_V1.0

UG050006_Titan2 Family FPGAs InputOutput Interface (IO) UserGuide_V1.0 2025.09.17

2025.09.17

-

UG050005_Titan2 Family FPGAs Configuration User Guide_V1.3

UG050005_Titan2 Family FPGAs Configuration User Guide_V1.3 2025.09.17

2025.09.17

-

UG050004 Titan2 Family FPGAs Clock Resources (Clock) User Guide_V1.3

UG050004 Titan2 Family FPGAs Clock Resources (Clock) User Guide_V1.3 2025.09.17

2025.09.17

-

UG050003_Titan2 Family FPGAs Arithmetic Process Module (APM) User Guide_V1.1

UG050003_Titan2 Family FPGAs Arithmetic Process Module (APM) User Guide_V1.1 2025.09.17

2025.09.17

-

UG050002_Titan2 Family FPGAs Dedicated RAM Module (DRM) User Guide_V1.2

UG050002_Titan2 Family FPGAs Dedicated RAM Module (DRM) User Guide_V1.2 2025.09.17

2025.09.17

-

UG050001_Titan2 Family FPGAs Configurable Logic Module (CLM) User Guide_V1.2

UG050001_Titan2 Family FPGAs Configurable Logic Module (CLM) User Guide_V1.2 2025.09.17

2025.09.17

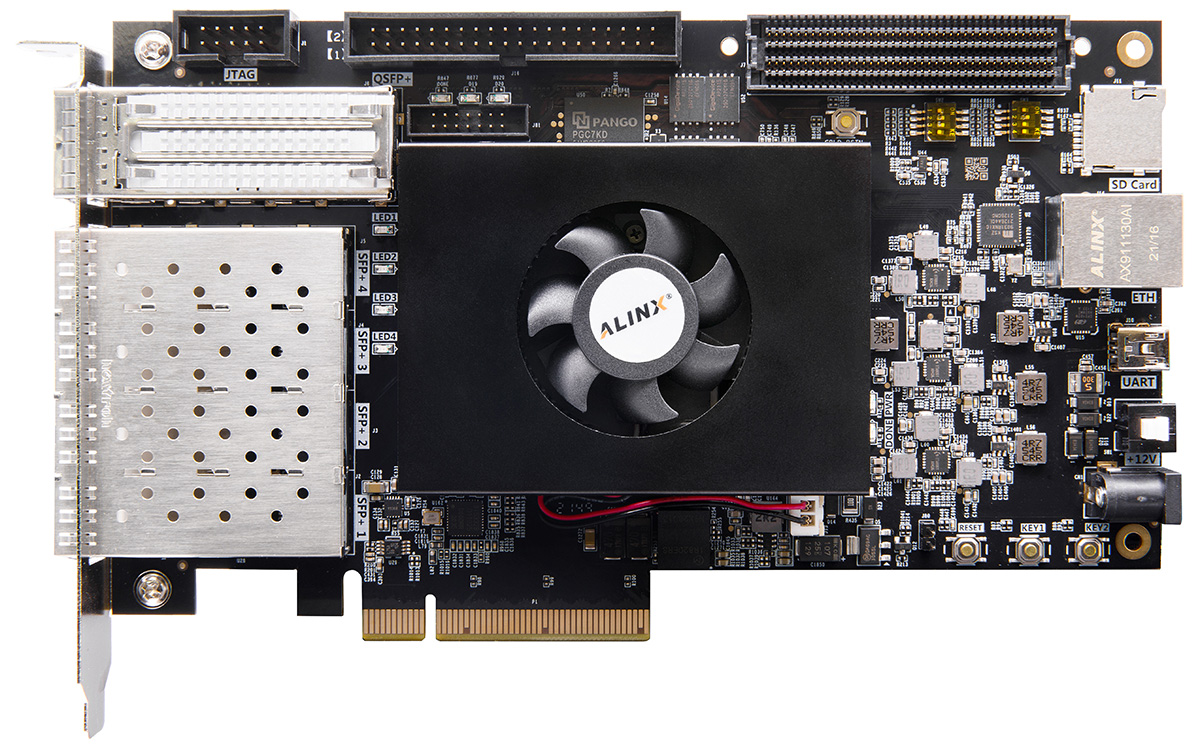

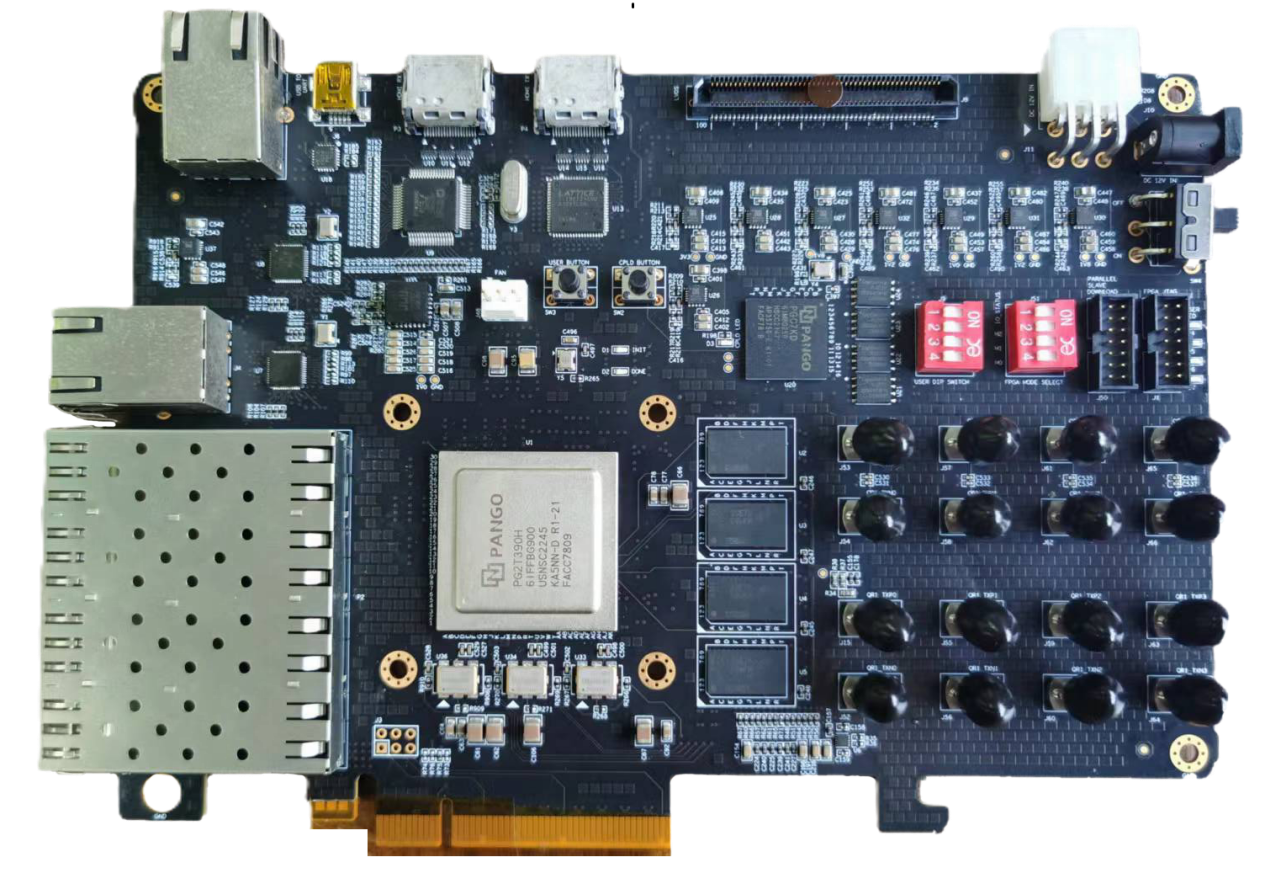

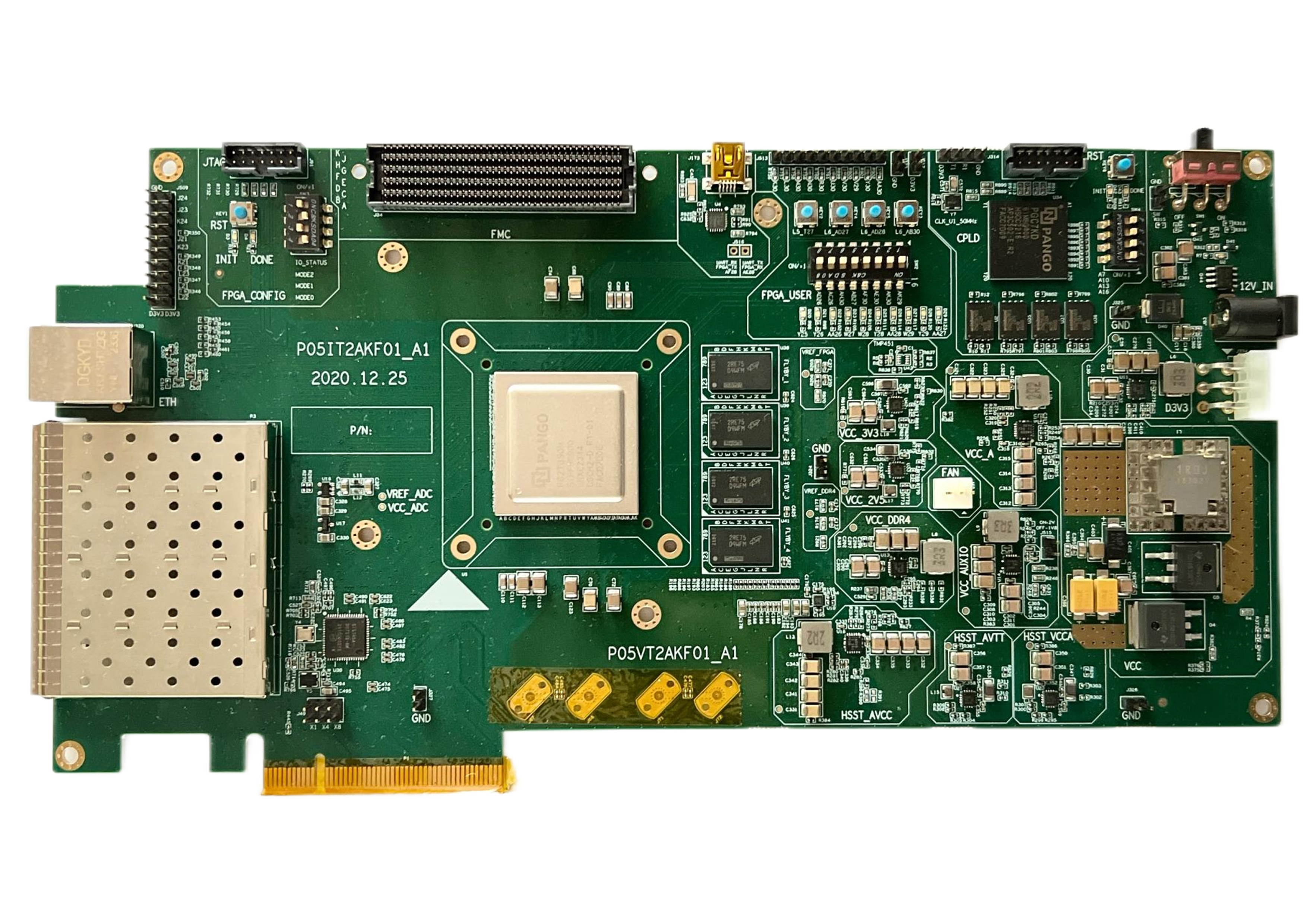

Development Boards and Kits

- Products Titan Family Logos Family Compa Family Pango Design Suite

- Solutions Communication Industrial Image&Video Consumer Auto Data center Other

- Resource Software and license IP Partners

- About us Company profile Contact us Announcement

-

Contact us

86-755-66886188

[email protected]

No. 15, Gaoxin South Road,

High-Tech Industrial Park,

Nanshan District, Shenzhen

Official public account

Official public account

©2023 All Rights Reserved Shenzhen Pango Microsystems Co., Ltd. Guangdong ICP Filing No. 14029535